| throughput | 1pixe/clock, 4pixel/clock |

| Image size | 320x240P~4096x2160P. Must be multiple of 4 in case of 4pixel/clock |

| color format | 8bit YUV444, 8bit YUV422 |

| Video signal interface | ・valid/ready signal handshake in AXI4-stream standard compliant

・Fixing the ready of master to high, fixed cycle delay operation by DE (data enable) is possible |

| Control interface | APB3 |

The figure below shows an example to integrate this IP between an image sensor and DRAM. This IP starts with a vertical sync event signal, and operates using a DE (data enable) signal. This IP operates with a fixed latency.

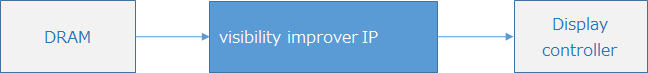

The figure below shows an example to integrate this IP between DRAM and a display controller. This IP starts with a vertical sync event signal, and operates using valid/ready handshake signals. If the display controller is unable to accept video data during horizontal blanking period and master ready signal goes low, this IP stops operating and stops requesting for read data to the DRAM, and resumes operating when master ready signal goes high again.

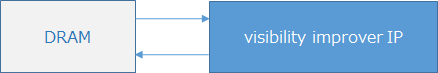

The figure below shows an example to integrate this IP between DRAM read and DRAM write. This IP starts with a vertical sync event signal or a software instruction, and operates using valid/ready handshake signals. This IP stops operation and resumes, according to DRAM response.

Click here for a brochure